Storm7

Newbie level 3

Hi guys,

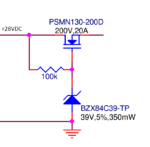

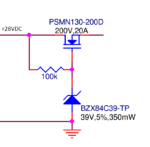

I'm looking for some help in further understanding how this active surge clamp works. The nominal input voltage for the system is 28V and the surge voltage is 80V for 100ms. The output is clamped to ~36V to protect everything downstream.

The Vth of the N-FET is 4V. I've ran some simulations in SIMetrix and I can see that it clamps the surge as desired. I was confused that it didn't show the N-FET conducting during nominal operation...

Any input?

Thanks!

I'm looking for some help in further understanding how this active surge clamp works. The nominal input voltage for the system is 28V and the surge voltage is 80V for 100ms. The output is clamped to ~36V to protect everything downstream.

The Vth of the N-FET is 4V. I've ran some simulations in SIMetrix and I can see that it clamps the surge as desired. I was confused that it didn't show the N-FET conducting during nominal operation...

Any input?

Thanks!