madhusmita99

Newbie

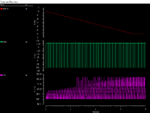

Actually I am working on VCO based ADC in 180nm technology . I have some doubts related to that topic.

1.I am not getting the correct output after DAC when ramp and sine inputs are applied. so kindly let me know how u got the correct output

2. I have set the DAC (Vref=1,Vrise=0 ,Vfall=0,Vdelay=0,Vtran=.9)

3. I have set the clk frequency of 16.11 MHz .(vpulse period is 62ns and pulse width is 60ns) i.e reset signal to the counter

4. I have used ramp signal of duration 3.4u

(when time=0s, v1=1v

when time=3.4us, v1=400mv.). ADC count maximum when control volatge is .4vand minimum when voltage is 1v.

Kindly suggest the time duration of ramp so that i will get correct result.

1.I am not getting the correct output after DAC when ramp and sine inputs are applied. so kindly let me know how u got the correct output

2. I have set the DAC (Vref=1,Vrise=0 ,Vfall=0,Vdelay=0,Vtran=.9)

3. I have set the clk frequency of 16.11 MHz .(vpulse period is 62ns and pulse width is 60ns) i.e reset signal to the counter

4. I have used ramp signal of duration 3.4u

(when time=0s, v1=1v

when time=3.4us, v1=400mv.). ADC count maximum when control volatge is .4vand minimum when voltage is 1v.

Kindly suggest the time duration of ramp so that i will get correct result.