krystalx

Newbie level 2

Hi guys, I'm new to Primetime and also not very familiar with some basic MOS technology.

I'm now trying to figure out one circuit, too see if it might have IR drop problems or something.

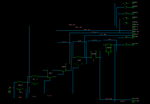

The circuit schematic is as followed **broken link removed**

We got 7 DFFs in a row, and each stage got its Q port connected to CK of next stage.

Right here Im trying to see if the transition time will be too large to cause IR drop or Tsetup/Thold violation

so first create_clock, set_clock_transition, and then figured out I have to set generated clocks to make CLK input of next stage works.

Clock Period Waveform Attrs Sources

-------------------------------------------------------------------------------

CLK 20.00 {0 10} p {CLK}

CLK2 40.00 {0 20} p, G {dff_basic1/Q}

CLK3 80.00 {0 40} p, G {dff_basic2/Q}

CLK4 160.00 {0 80} p, G {dff_basic3/Q}

CLK5 320.00 {0 160} p, G {dff_basic4/Q}

CLK6 640.00 {0 320} p, G {dff_basic5/Q}

CLK7 1280.00 {0 640} p, G {dff_basic6/Q}

Generated Master Generated Master Waveform

Clock Source Source Clock Modification

-------------------------------------------------------------------------------

CLK2 CLK dff_basic1/Q CLK div(2)

CLK3 dff_basic1/Q dff_basic2/Q CLK2 div(2)

CLK4 dff_basic2/Q dff_basic3/Q CLK3 div(2)

CLK5 dff_basic3/Q dff_basic4/Q CLK4 div(2)

CLK6 dff_basic4/Q dff_basic5/Q CLK5 div(2)

CLK7 dff_basic5/Q dff_basic6/Q CLK6 div(2)

idk if I set these clocks correctly, cuz I dont see transition time getting longer in each stage, and the report shows the slack in each stage are the same, which means the transition time of the input clock didnt change through each stage.

Is it because I set the generated clock wrong? or the transition time not correct?

I'm now trying to figure out one circuit, too see if it might have IR drop problems or something.

The circuit schematic is as followed **broken link removed**

We got 7 DFFs in a row, and each stage got its Q port connected to CK of next stage.

Right here Im trying to see if the transition time will be too large to cause IR drop or Tsetup/Thold violation

so first create_clock, set_clock_transition, and then figured out I have to set generated clocks to make CLK input of next stage works.

Clock Period Waveform Attrs Sources

-------------------------------------------------------------------------------

CLK 20.00 {0 10} p {CLK}

CLK2 40.00 {0 20} p, G {dff_basic1/Q}

CLK3 80.00 {0 40} p, G {dff_basic2/Q}

CLK4 160.00 {0 80} p, G {dff_basic3/Q}

CLK5 320.00 {0 160} p, G {dff_basic4/Q}

CLK6 640.00 {0 320} p, G {dff_basic5/Q}

CLK7 1280.00 {0 640} p, G {dff_basic6/Q}

Generated Master Generated Master Waveform

Clock Source Source Clock Modification

-------------------------------------------------------------------------------

CLK2 CLK dff_basic1/Q CLK div(2)

CLK3 dff_basic1/Q dff_basic2/Q CLK2 div(2)

CLK4 dff_basic2/Q dff_basic3/Q CLK3 div(2)

CLK5 dff_basic3/Q dff_basic4/Q CLK4 div(2)

CLK6 dff_basic4/Q dff_basic5/Q CLK5 div(2)

CLK7 dff_basic5/Q dff_basic6/Q CLK6 div(2)

idk if I set these clocks correctly, cuz I dont see transition time getting longer in each stage, and the report shows the slack in each stage are the same, which means the transition time of the input clock didnt change through each stage.

Is it because I set the generated clock wrong? or the transition time not correct?