Kosyas41

Member level 3

Hello,

I have a problem with connection of two signals,im using VHDL

first signal has fsin_o : out std_logic_vector(15 downto 0);

second signal out_imag : out signed(OUTPUT_WIDTh-1 downto 0);

OUTPUT_WIDTH: positive := 16;

i want to connect like this fsin_o => out_imag

Could you please help me or give idea how to do it?

Quartus show me this error

I have a problem with connection of two signals,im using VHDL

first signal has fsin_o : out std_logic_vector(15 downto 0);

second signal out_imag : out signed(OUTPUT_WIDTh-1 downto 0);

OUTPUT_WIDTH: positive := 16;

i want to connect like this fsin_o => out_imag

Could you please help me or give idea how to do it?

Quartus show me this error

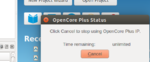

Code:

Error (10476): VHDL error at bladerf-hosted.vhd(744): type of identifier "out_imag" does not agree with its usage as "std_logic_vector" type

Last edited: