Peiqii

Newbie level 6

Hi There,

I am going to do a RF energy-harvesting prototype system. However, I face some problems which are:

1. Which type of matching network (between Antenna and rectifier) is suggested to use?

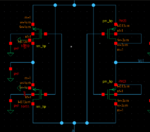

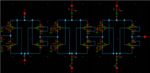

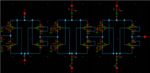

2. How to calculate the input impedance of the rectifier? The rectifier design is using the MOSFET transistor as the diagram below. I have no idea on calculating it.

Kindly advise. Thanks!

Regards

Peiqii

I am going to do a RF energy-harvesting prototype system. However, I face some problems which are:

1. Which type of matching network (between Antenna and rectifier) is suggested to use?

2. How to calculate the input impedance of the rectifier? The rectifier design is using the MOSFET transistor as the diagram below. I have no idea on calculating it.

Kindly advise. Thanks!

Regards

Peiqii