Debdut

Full Member level 3

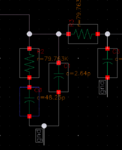

I am designing a PLL with a LC-VCO. The frequency control of the VCO is done through drain-source connected n-moscap. The output of the loop filter is going to the moscap drain-source and the gate of the moscap is going to the VCO.

When the loop is running the oscillation frequency of the VCO is getting coupled though the moscap to the loop filter. Even after the loop is locked I am getting oscillations at the loop filter output. Needless to say that spurs are generated due to this...

How can I isolate the loop filter from the moscap?

When the loop is running the oscillation frequency of the VCO is getting coupled though the moscap to the loop filter. Even after the loop is locked I am getting oscillations at the loop filter output. Needless to say that spurs are generated due to this...

How can I isolate the loop filter from the moscap?