electronicman26

Full Member level 2

Hi

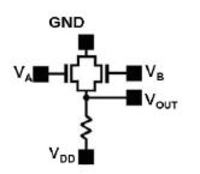

I want to compare a logic gate (for example nand,or,and,not,...) performance based on mosfet with the same based on ofet

now I have several question:

1-should the circuit topology be same in mosfet and ofet based?

2-is it correct that compare 0.18um mosfet with ofet that has 25um length?

I want to compare a logic gate (for example nand,or,and,not,...) performance based on mosfet with the same based on ofet

now I have several question:

1-should the circuit topology be same in mosfet and ofet based?

2-is it correct that compare 0.18um mosfet with ofet that has 25um length?