preethi19

Full Member level 5

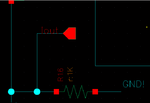

Hi initially wen doing layout in cadence i used VSS and gnd on the same substrate and got the error "label/pin on a net with differnet name". I got the suggestion to add a dnw layer and isolate the two. I put VSS within the dnw and outside gnd and the error was cleared. But now to get the output from a transistor's drain i need to drive it through a load resistor of 1K. And so i connect one end of resistor to drain of transistor and place a output pin 'Iout' on that metal. The other end of resistor is grounded. And in layout resistor is in a n well with a bulk layer which i gave it to VDD. Now i am getting the same above error between 'gnd' and 'Iout'.

Vss and gnd i can understand the input potential to same p-substrate. but why between gnd and iout??? Can anyone plsss tell me how to correct this. I wasn't sure if the method was right but i tried using dnw around resistor.. Still didnt work.. Pls help!!!!

Vss and gnd i can understand the input potential to same p-substrate. but why between gnd and iout??? Can anyone plsss tell me how to correct this. I wasn't sure if the method was right but i tried using dnw around resistor.. Still didnt work.. Pls help!!!!

Last edited: