preethi19

Full Member level 5

Hi i have attached an image of two transistors connected. Could anyone pls tell me what type of function it does. it looks to be like a current mirror

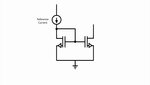

Its equivalent layout is der to the right of the image. My question is i thought current mirror has a structure like the following image

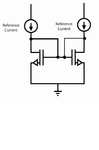

Wer the gates of two transistors are connected and to one of the transistor's drain the current source is given that needs to be copied to the other transistor. But in the first image the two transitors connection is something like this

So why is this current mirror like this. Secondly if its a current mirror i thought they need to me matched since they perfom the same function. Why is this not matched in the layout? Maybe current mirror needs matching so current is copied properly. but for the first image it looks like there is steady supply of current to both the transistors so they ignored the matching. Suppose in my case i have a current mirror like the second image then am i supposed to do matching or just use two transistors like the first image layout. It looks like they have just laid it out as

s A d B s which is A | B

so in my case can i do it like above or should i make it as A B | B A.... Can someone pls help!!!

Its equivalent layout is der to the right of the image. My question is i thought current mirror has a structure like the following image

Wer the gates of two transistors are connected and to one of the transistor's drain the current source is given that needs to be copied to the other transistor. But in the first image the two transitors connection is something like this

So why is this current mirror like this. Secondly if its a current mirror i thought they need to me matched since they perfom the same function. Why is this not matched in the layout? Maybe current mirror needs matching so current is copied properly. but for the first image it looks like there is steady supply of current to both the transistors so they ignored the matching. Suppose in my case i have a current mirror like the second image then am i supposed to do matching or just use two transistors like the first image layout. It looks like they have just laid it out as

s A d B s which is A | B

so in my case can i do it like above or should i make it as A B | B A.... Can someone pls help!!!