DanyR

Member level 3

- Joined

- Aug 23, 2015

- Messages

- 67

- Helped

- 6

- Reputation

- 12

- Reaction score

- 6

- Trophy points

- 8

- Location

- Nieuwpoort, Belgium

- Activity points

- 677

LTSpice simple model for grid tied invertor

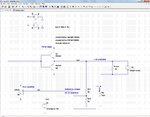

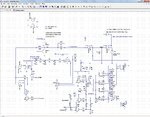

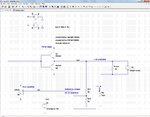

Hi, I am learning to work with LTSpice and I am also very interested about the "how" of grid tied invertors, so I decided to make a very simplified and basic circuit diagram in LtSpice that could be simulated.

Reference see https://www.edaboard.com/threads/345807/.

The starting points were:

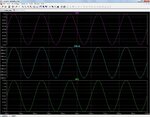

- the invertor deliveres a constant current to the grid/load of 2A peak (AC)

- the current is in phase with the grid voltage

- the grid is always connected and stable

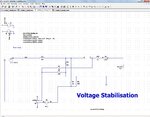

The circuit presented lacks a lot of stuff that should be added later:

- the PWM drive of the output transistors (power stage) + addition of the PWM filter of course

- circuitry to startup/connect/disconnect the invertor in a safe way

- stabilisation of the AC reference voltage (Vin in the diagram)

- a way to make the constant output current changeable

- feed and adapt the power curcuit (and others if necessary) so that it can cope with a grid voltage of 230Vac.

- safety circuitry e.g. in case the grid gets disconnected etc...

In the circuit diagram only a grid voltage of 10V peak was used (V5).

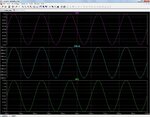

The load (of e.g. the whole household) is represented by RLoad and draws 0.5A AC peak. This means that, when the invertor delivers 2A AC peak, the grid (V5) will be fed with 1.5A peak AC.

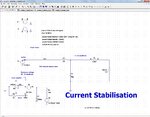

How it works:

The AC reference voltage is made with R11 and R12, and is stable since the VGrid (V5) does not change in this simulation. Additionally the derivation of the reference from the grid with a simple R voltage divider ensures the current delivered out of the invertor will be in phase with the grid voltage.

A series resistor in the output of the invertor (R2) is used to measure the current delivered by the invertor. The voltage across it (0.01V/A) is amplified 100 times with B1 (voltage controlled voltage source), wich gives an 1V/A sensivity at comparator U4. The latter compares that current derived voltage with the reference voltage...

Hi, I am learning to work with LTSpice and I am also very interested about the "how" of grid tied invertors, so I decided to make a very simplified and basic circuit diagram in LtSpice that could be simulated.

Reference see https://www.edaboard.com/threads/345807/.

The starting points were:

- the invertor deliveres a constant current to the grid/load of 2A peak (AC)

- the current is in phase with the grid voltage

- the grid is always connected and stable

The circuit presented lacks a lot of stuff that should be added later:

- the PWM drive of the output transistors (power stage) + addition of the PWM filter of course

- circuitry to startup/connect/disconnect the invertor in a safe way

- stabilisation of the AC reference voltage (Vin in the diagram)

- a way to make the constant output current changeable

- feed and adapt the power curcuit (and others if necessary) so that it can cope with a grid voltage of 230Vac.

- safety circuitry e.g. in case the grid gets disconnected etc...

In the circuit diagram only a grid voltage of 10V peak was used (V5).

The load (of e.g. the whole household) is represented by RLoad and draws 0.5A AC peak. This means that, when the invertor delivers 2A AC peak, the grid (V5) will be fed with 1.5A peak AC.

How it works:

The AC reference voltage is made with R11 and R12, and is stable since the VGrid (V5) does not change in this simulation. Additionally the derivation of the reference from the grid with a simple R voltage divider ensures the current delivered out of the invertor will be in phase with the grid voltage.

A series resistor in the output of the invertor (R2) is used to measure the current delivered by the invertor. The voltage across it (0.01V/A) is amplified 100 times with B1 (voltage controlled voltage source), wich gives an 1V/A sensivity at comparator U4. The latter compares that current derived voltage with the reference voltage...