anushaas

Member level 5

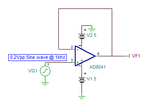

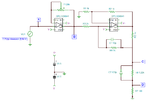

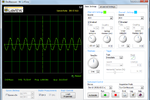

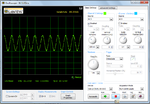

I am using an AD8041 IC as a buffer for a 0.2Vpp sinewave input at 1kHz from the function generator.The circuit is set on an NI Elvis II+ board.The buffer is unloaded but there occurs some offset at the output of the buffer.

Why is this happening?

Why is this happening?