Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

- - - Updated - - -

I'll try this approach. Do you have any source for the design procedure.

Which one? Subthreshold region operation for M5 (simple method) or NMOS/PMOS parallel rail-to-rail input architecture (more complex)? The paper which I linked above shows the latter method.

And don't forget to reveal your process size and your previous schematic, incl. W/L sizes.

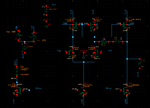

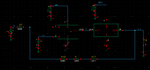

I want to try "Subthreshold region operation for M5 (simple method)". I have attached the screenshot of my design where i achevied min ICMR of 1V but i need to get it to 0.6V. My design is based on 180nm technology and VDD is 3.3V.

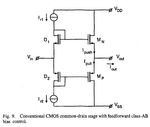

Also from the paper suggested by you I found the the class ab output stage(image atached), which i am planning to implement for my design with output voltage range of 0 to 40V. Where i would be using HVMOS. So is it possible with this architecture?

Yes, I think this should be possible if you can renounce on two diode voltages and two drain-source saturation voltages

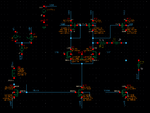

Of course: R9 + R8 are in parallel to R11 (V3 has an output impedance of 0Ω), so your adjusted gain is around 100 , not 10 as you probably intended.I tried this class ab output stage today. But i am having a clipped output.

I tried giving a negative feedback, but the problem i am facing problem with keeping the input bias voltage to 2V. due to which the + and - input nmos are not baised at same voltage and the bias of the further stages goes wrong. Could you suggest me with the feedback topolgy

Remove V3 (and perhaps replace R8 and R9 by wires, they aren't necessary),

Then what would be the calculation for gain. As for negative feedback the gain is Rf/Rin, but if i replace by wire how wud be the gain calculation.

What I suggested was for the test bench; for application you need a different setup, depending on using your opamp as an inverting or a non-inverting amplifier. If you use it in non-inverting mode (input to VIP), its gain would be 1+(R10/R11). Of course you have to provide the correct DC bias to VIP also - same as in the inverting mode case.

But when i changed the resistor values to obtain gain of 18X which is my required gain, I am getting a weird output.

Please suggest how would i get gain of 18X by using the feedback