DJP1992

Newbie level 5

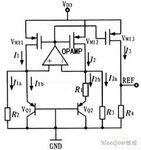

Hi ,everyone i am trying to design a low voltage BGR.I am using 90nm Technology with 1v supply and vref is 700mV.Eventhough,I am getting variation of around 8mV across corners(SS,NN,SF,FS,FF) but vref curve is inverted parabola(i.e. U)(vref v/s temp).I am not able to figure out what may be the possible reason.Can anyone help me out.

Obtained output:

Phase margin=72 deg

PSRR=-38dB

IS the output acceptable or is it compulsory that we must get normal parabola(inverted U) curve.