amsdesign

Member level 3

Hello everyone,

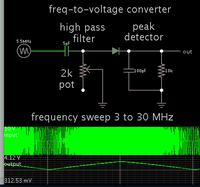

I have a clock signal that varies from 10Mhz- 100Mhz and I need to generate a voltage proportional to the frequency as it varies in step size of 50kHz.

Is there any way to accomplish this? Would a simple RC High pass filter solve the problem?

Edit: I'm not looking for any IC. I want a circuit to perform the job

I have a clock signal that varies from 10Mhz- 100Mhz and I need to generate a voltage proportional to the frequency as it varies in step size of 50kHz.

Is there any way to accomplish this? Would a simple RC High pass filter solve the problem?

Edit: I'm not looking for any IC. I want a circuit to perform the job

Last edited: