amsdesign

Member level 3

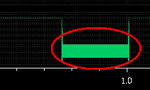

Hi I'm trying to simulate the dead-zone present in the phase frequency detector of a PLL. However, I get these waveforms

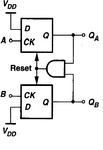

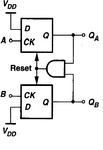

Here is the circuit diagram of the phase frequency detector. The FFs in my simulation have a reset that need to be set to LOW. So I'm using a NAND gate and Z is the output of the NAND gate.

However, for any amount of phase shift, I see ringing on the nodes. Why exactly is this happening?

Here is the circuit diagram of the phase frequency detector. The FFs in my simulation have a reset that need to be set to LOW. So I'm using a NAND gate and Z is the output of the NAND gate.

However, for any amount of phase shift, I see ringing on the nodes. Why exactly is this happening?

Last edited by a moderator: