mr_sophisticated

Newbie level 4

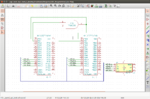

I would like to transmit data from a pic18f to another pic18f via an external ram . The ram needs to accomadate data from pic1 and transmit it to pic2 when called for ; if possible simultaneously too . The ram size shall be 1-2 Mb .

I have gone through immense application notes on pic to pic communication and pic to external ram communication but failed to get detailed documentation on pic to pic communication via a memory element .

My intention of using RAM is ofcourse for extended space , faster speed , adding option for parallel and serial communication and for independently communicating to pic1 and pic2 .

I have gone through immense application notes on pic to pic communication and pic to external ram communication but failed to get detailed documentation on pic to pic communication via a memory element .

My intention of using RAM is ofcourse for extended space , faster speed , adding option for parallel and serial communication and for independently communicating to pic1 and pic2 .