Muhammad Moiz khan

Newbie level 4

Hello my question is that what are the switching conditions for FET. Thanks

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

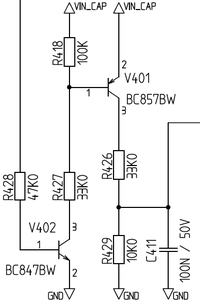

In short words: The driver need to have enough peak current to quickly charge the gate capacitance, the supplied voltage to gate has to be higher than VTH.what are the switching conditions for FET

I agree that the title reminds to SMPS application, but read post #6 to see that the problem is completely different.read the "high speed mosfet gate drive" article by Laszlo balogh...that mightn't be the exact name of the article but it answers about switching fets..I presume you mean for SMPS use?

That's how a PJFET works. It's source is connected to Vbat. Consider that the more positive channel terminal acts as source, not the nominal one.why we have to give 4V above Vbat?