Ashish Agrawal

Member level 3

Hi All,

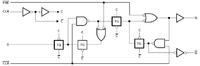

I am trying to understand the reset recovery and removal time in a flop architecture (made up of back to back inverters and transmission gates). Can anyone help me where and how to connect reset pin in a flop architecture?

Basically I am trying to compare with recovery/removal time with setup/hold time, and also want to understand why it is needed only during de-assertion of reset.

I am referring the following link to understand the setup/hold time

https://www.edn.com/design/analog/4371393/Understanding-the-basics-of-setup-and-hold-time

Regards,

Ashish

I am trying to understand the reset recovery and removal time in a flop architecture (made up of back to back inverters and transmission gates). Can anyone help me where and how to connect reset pin in a flop architecture?

Basically I am trying to compare with recovery/removal time with setup/hold time, and also want to understand why it is needed only during de-assertion of reset.

I am referring the following link to understand the setup/hold time

https://www.edn.com/design/analog/4371393/Understanding-the-basics-of-setup-and-hold-time

Regards,

Ashish