GIGER

Junior Member level 1

Hello guys.

I have a problem.

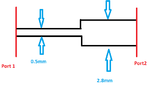

I'm designing a microstrip line and I have to put a step between two different lines as you can see in the uploaded figure.

The simulated results are not any good and i want to ask if anyone knows a solution to this problem. Possibly a cut or whatever.

Thank you very much!

I have a problem.

I'm designing a microstrip line and I have to put a step between two different lines as you can see in the uploaded figure.

The simulated results are not any good and i want to ask if anyone knows a solution to this problem. Possibly a cut or whatever.

Thank you very much!