jimmykk

Full Member level 3

Hi

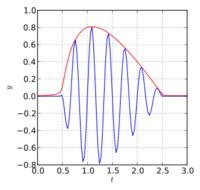

I have a problem getting output from DAC AD5641(14-BIT). Input first goes from adc(LTC2245) to Fpga and negative cycle gets removed and output should come from dac. Input is .5V 200khz , clock 5mhz. can someone tell me where am i doing wrong. Output should be only a pos cycle of input.

Thanks

I have a problem getting output from DAC AD5641(14-BIT). Input first goes from adc(LTC2245) to Fpga and negative cycle gets removed and output should come from dac. Input is .5V 200khz , clock 5mhz. can someone tell me where am i doing wrong. Output should be only a pos cycle of input.

Thanks

Code VHDL - [expand]

Last edited by a moderator: