EHY

Member level 1

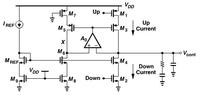

I designed Charge pump like attached image.

I designed Charge pump like attached image.When UP signal is turn on (width 100ps) current of pink color node switching quite properly.

but problem is that mirroring current of UP current(blue color node) is not fast switching.

so how can i increase switching speed of bule color node current??

i want to increase length of MOSFET to decrease UP/DN current mismatch.