hm1622

Junior Member level 1

I dont know from where to start so guys help me with that. i am beginner in RTL design

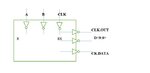

please help me with RTL(verilog) design of this block.i have some specification

like

• X means a minimum size width for n and p channel transistor width for

the transistors inside the inverter .

• 8X means n and p ch widths are 8 times that of 1X inverter.

• D<9:0> means data lines; these are digital outputs that change after the clock rising edge. Think of it as a digital bus.