dshoter13

Member level 4

Hi.

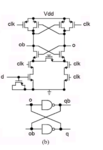

I'm trying to design the following Sense-Amplifier Flip-Flop

I'm using TSMC 90nm CMOS technology, and I'm having troubles doing the design. I'm not getting what I expect at the output node.

Can anyone give me some ideas about the correcto sizing of the transistors? I'm trying to achieve a low metastability region, and a low Clock-to-Q delay.

The out is the Q, fast correspondes to the D and slow is the Clock.

Thank you for your atention.

Best regards.

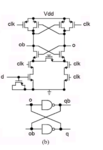

I'm trying to design the following Sense-Amplifier Flip-Flop

I'm using TSMC 90nm CMOS technology, and I'm having troubles doing the design. I'm not getting what I expect at the output node.

Can anyone give me some ideas about the correcto sizing of the transistors? I'm trying to achieve a low metastability region, and a low Clock-to-Q delay.

The out is the Q, fast correspondes to the D and slow is the Clock.

Thank you for your atention.

Best regards.