omerysmi

Member level 5

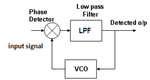

Hello, I need help in understanding the operation of PLL as FM Detector.

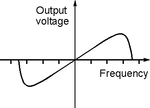

This is the graph of the output voltage as a function of the frequency of the input signal:

Suppose that:

- the amplitude of the input signal is 4v.

- f0 is 100kHz.

As we can see when the frequency of the input signal is equal to f0 we will get in the output of the LPF 0V.

My question is, if we will change the frequency of the input signal to the lock frequency (you can see where is it in the graph) , the voltage in the output of the LPF will be 4V? (I know that after fLock1 and fLock2 the voltage will be zero of course as we can see in the graph).

This is the graph of the output voltage as a function of the frequency of the input signal:

Suppose that:

- the amplitude of the input signal is 4v.

- f0 is 100kHz.

As we can see when the frequency of the input signal is equal to f0 we will get in the output of the LPF 0V.

My question is, if we will change the frequency of the input signal to the lock frequency (you can see where is it in the graph) , the voltage in the output of the LPF will be 4V? (I know that after fLock1 and fLock2 the voltage will be zero of course as we can see in the graph).