je01911

Junior Member level 1

Hi all,

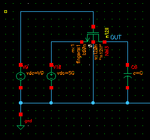

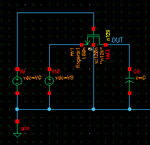

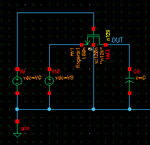

I am conducting simple noise simulation like

using parametric simulation I sweeps the gate (VG) and input (VS) voltage and load capacitance(C).

According to theory, the thermal noise depends on load capacitance.

Therefore, the noise power is not related with gate and input voltages.

Because load capacitance is multiplier of 10 (100f, 1p, 10p, 100p, 1nF), the thermal noise should be (4.14*10^x V²/Hz) (x is ..., -9, -10, -11 ... ) in all case.

And I expect of

41.4nV²/Hz at 100fF

4.14nV²/Hz at 1pF

0.414nV²/Hz at 10pF

41.4pV²/Hz at 100pF

4.14pV²/Hz at 1nF

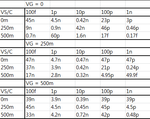

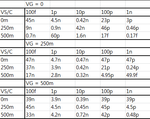

However, the simulation results show like

the unit of noise is V²/Hz

In many cases, the simulated results depart from theory result.

Do you know the reason ? and is It reliable results?

I am conducting simple noise simulation like

using parametric simulation I sweeps the gate (VG) and input (VS) voltage and load capacitance(C).

According to theory, the thermal noise depends on load capacitance.

Therefore, the noise power is not related with gate and input voltages.

Because load capacitance is multiplier of 10 (100f, 1p, 10p, 100p, 1nF), the thermal noise should be (4.14*10^x V²/Hz) (x is ..., -9, -10, -11 ... ) in all case.

And I expect of

41.4nV²/Hz at 100fF

4.14nV²/Hz at 1pF

0.414nV²/Hz at 10pF

41.4pV²/Hz at 100pF

4.14pV²/Hz at 1nF

However, the simulation results show like

the unit of noise is V²/Hz

In many cases, the simulated results depart from theory result.

Do you know the reason ? and is It reliable results?