MahmoudHassan

Full Member level 6

Hello

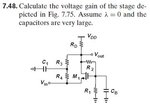

while i was solving problems in Common gate amplifier i found this one

Figure 1 is the problem

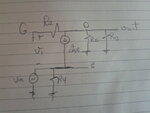

Figure 2,3 my solution and small signal model

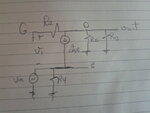

Figure 4 is the solution manual solution

i doubt that solution manual is not correct because it is supposed that all capacitors must be shorted (i.e as the problem that capacitors are very large) which will simplify the problem too much

i hope you can help me to know what is wrong with my analysis and why solution manual solved it like that

Thanks

.

while i was solving problems in Common gate amplifier i found this one

Figure 1 is the problem

Figure 2,3 my solution and small signal model

Figure 4 is the solution manual solution

i doubt that solution manual is not correct because it is supposed that all capacitors must be shorted (i.e as the problem that capacitors are very large) which will simplify the problem too much

i hope you can help me to know what is wrong with my analysis and why solution manual solved it like that

Thanks

.