galenthas

Newbie level 3

Hello all,

Through my frustrations and heading back here over and over again for references and suggestions today I'm posting my first thread here in need of desperate help.

I had a similar problem with costas loop before. I then scratched my head against the walls (i know i am not that bright) and learned the theory nehind the loop filter and vco and stuff and implemented a model with system generator that operates @ 300 MHz and capable of tracking b-q-8-psk signals. I know its no big deal.

So i thought i could implement the timing recovery now with some work, but I couldn't. I have studied the papers, simulink models, reference hdl codes.

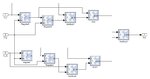

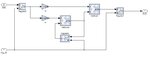

Ok, i am trying to implement the timing recovery circuit with gardner ted. I have the blocks all ready; gardner ted, loop filter, vco and all that but when put together they simply don't work. I even tried direct conversion of the matlab simulink demo to vhdl but i am missing something.

My gardner ted samples twice the symbol rate and outputs the correspoing error. I have my loop filter parameters (which i believe is not the cause of my problem). I implemented the vco with good sensitivity and correct center frequency.

Do you have any suggestions for me? Should i do more reading? Or did you have such experience?

Regards.

Through my frustrations and heading back here over and over again for references and suggestions today I'm posting my first thread here in need of desperate help.

I had a similar problem with costas loop before. I then scratched my head against the walls (i know i am not that bright) and learned the theory nehind the loop filter and vco and stuff and implemented a model with system generator that operates @ 300 MHz and capable of tracking b-q-8-psk signals. I know its no big deal.

So i thought i could implement the timing recovery now with some work, but I couldn't. I have studied the papers, simulink models, reference hdl codes.

Ok, i am trying to implement the timing recovery circuit with gardner ted. I have the blocks all ready; gardner ted, loop filter, vco and all that but when put together they simply don't work. I even tried direct conversion of the matlab simulink demo to vhdl but i am missing something.

My gardner ted samples twice the symbol rate and outputs the correspoing error. I have my loop filter parameters (which i believe is not the cause of my problem). I implemented the vco with good sensitivity and correct center frequency.

Do you have any suggestions for me? Should i do more reading? Or did you have such experience?

Regards.