Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

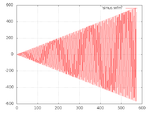

#!/usr/bin/env python

import math

from numpy import arange

def main():

fileName=open("sinus.wfm","w")

for i in arange(0,1800/math.pi,.1):

fileName.write("%f %f\n"%(i,(1+1*i*math.sin(i))))

fileName.close()

if __name__=="__main__":

main()