erece

Junior Member level 3

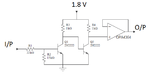

I want to convert a square wave with high level of 3.3 V & low level of 0V to a square wave of high level of 1.8 V and low level 0V. Frequency of square wave is 1 MHz in one case and 25 MHz in other case. I have the circuit for the converter as shown in the figure. I simulated this circuit both in LT Spice & Tina. The circuit simulation is working for 1MHz signal but with some delay. And it is not working for 25 MHz. May be because switching time of BJT is high as compared to period of the signal. Suggest some alternative for that or any modification in the circuit. And also I am reluctant to use any SMD level translator IC.