ruwan2

Member level 5

Hi,

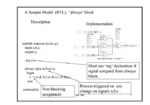

I am new to Verilog. Although there are already posts talking about blocking and nonblocking on line, it is still not sure to me on a specific example. I see one hand-out as:

It has "y=", but it shows non-blocking in the legend below. "y=" is a typo?

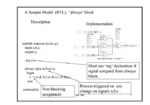

Then, I simulate this simple module in Modelsim. I do not see any difference with both "y=" and "y<=". Is this true (no difference here) for both simulation and synthesis?

The above example is from the link:

**broken link removed**

on slide 7 of page 2.

Thanks,

I am new to Verilog. Although there are already posts talking about blocking and nonblocking on line, it is still not sure to me on a specific example. I see one hand-out as:

It has "y=", but it shows non-blocking in the legend below. "y=" is a typo?

Then, I simulate this simple module in Modelsim. I do not see any difference with both "y=" and "y<=". Is this true (no difference here) for both simulation and synthesis?

The above example is from the link:

**broken link removed**

on slide 7 of page 2.

Thanks,

Last edited: