mpig09

Full Member level 4

Hi all:

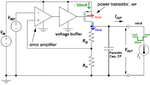

I am design a Capless LDO.

When I check the load regulator of the LDO,

the simulation result is strange:

the output voltage is negative value

when the load from light load to heavy load.

Please reference the attached file.

After check the current of the Power MOS (MP) during light load to heavy load,

The simulation shows the body outputs a current when the source and body are connect together.

On the other hand, remove the parasitic cap (CP), the LDO is work normal.

Based on the simulation result, I have some questions?

1. Is the simulation result correct (with/without CP)?

2. the cap how to cause the body of MP output a current?

Could anyone help me ?

Thanks.

mpig

I am design a Capless LDO.

When I check the load regulator of the LDO,

the simulation result is strange:

the output voltage is negative value

when the load from light load to heavy load.

Please reference the attached file.

After check the current of the Power MOS (MP) during light load to heavy load,

The simulation shows the body outputs a current when the source and body are connect together.

On the other hand, remove the parasitic cap (CP), the LDO is work normal.

Based on the simulation result, I have some questions?

1. Is the simulation result correct (with/without CP)?

2. the cap how to cause the body of MP output a current?

Could anyone help me ?

Thanks.

mpig