nats_

Newbie level 6

Hi,

i have two questions on this topic:

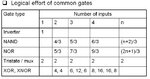

1. how do i calculate a delay of certain component, if all i know is its' input capacitance?

(i have no knowledge of any resistance or even the lines' impedance).

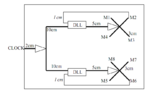

2. given a circuit with a DLL component (like in the image), how do i calculate the insertion delay?

thanks!

i have two questions on this topic:

1. how do i calculate a delay of certain component, if all i know is its' input capacitance?

(i have no knowledge of any resistance or even the lines' impedance).

2. given a circuit with a DLL component (like in the image), how do i calculate the insertion delay?

thanks!