DimaKilani

Member level 1

Hi everyone,

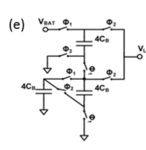

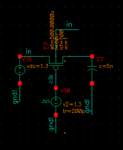

I'm designing a step down Switched Capacitor (SC) dc-dc converter. I'm using a spice simulation in order to observe the behavior of the circuit.

I want to calculate the power efficiency of the SC converter. efficiency=Pout/Pin. pout=Iou*Vout which is constant.

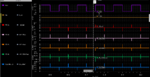

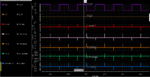

The problem here is the Pin since the current is fluctuating between negative microAmpere and positive microAmpere. So, in order to calculate the input power efficiency, I used the 1/T*integral (V*I). if we think about the integral, it means the area under the curve. this means that some negative values of the input power will cancel the positive values. and that will affect the power efficiency. Am afraid about this point.

Anyone has an idea about this problem. Is the input current of the of the SC converter is varying ? or maybe my design is wrong ..

Thanks,

Dima

I'm designing a step down Switched Capacitor (SC) dc-dc converter. I'm using a spice simulation in order to observe the behavior of the circuit.

I want to calculate the power efficiency of the SC converter. efficiency=Pout/Pin. pout=Iou*Vout which is constant.

The problem here is the Pin since the current is fluctuating between negative microAmpere and positive microAmpere. So, in order to calculate the input power efficiency, I used the 1/T*integral (V*I). if we think about the integral, it means the area under the curve. this means that some negative values of the input power will cancel the positive values. and that will affect the power efficiency. Am afraid about this point.

Anyone has an idea about this problem. Is the input current of the of the SC converter is varying ? or maybe my design is wrong ..

Thanks,

Dima