Liffs

Member level 1

I have a simple question about false paths: why do they exist? I mean, if they can never "happen", why does the synthesis tool generate (or keep) them?

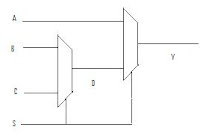

I'm not talking about asynchronous paths, but paths that will never really occur. Like this one: https://statictiminganalysis.blogspot.com.br/2007/06/what-is-false-path.html

Thanks in advance!

I'm not talking about asynchronous paths, but paths that will never really occur. Like this one: https://statictiminganalysis.blogspot.com.br/2007/06/what-is-false-path.html

Thanks in advance!