long88

Member level 3

Hi All,

Recently , i am doing some test with the super capacitor. My objectives was to prove that the time taken to discharge a super capacitor from 3.3 - 1.8 v is equal to my calculation results.

Let assume that the current discharge to my load is constant at 5uA. The capacitor is 3.3v and 5F.

Based on my calculation, the time taken for a capacitor voltage drop from 3.3 - 1.8 V is 2500000 seconds.

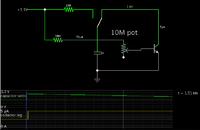

However, the current drop will always drop if the voltage drop. I need a circuit that can withdraw constant current within the voltage range of (3.3 - 1.8v). Is anyone can recommend me some simple constant current load?

THank you very much.

Recently , i am doing some test with the super capacitor. My objectives was to prove that the time taken to discharge a super capacitor from 3.3 - 1.8 v is equal to my calculation results.

Let assume that the current discharge to my load is constant at 5uA. The capacitor is 3.3v and 5F.

Based on my calculation, the time taken for a capacitor voltage drop from 3.3 - 1.8 V is 2500000 seconds.

However, the current drop will always drop if the voltage drop. I need a circuit that can withdraw constant current within the voltage range of (3.3 - 1.8v). Is anyone can recommend me some simple constant current load?

THank you very much.