Osawa_Odessa

Banned

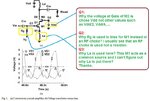

Hi,

I am studying the article "A 2.4-GHz 0.18-um CMOS Self-Biased Cascode Power Amplifier" (attached). Here are what I am confused. Please help. Thank you.

I am studying the article "A 2.4-GHz 0.18-um CMOS Self-Biased Cascode Power Amplifier" (attached). Here are what I am confused. Please help. Thank you.