wakeup12

Newbie level 3

Hello,

I just registered for the forum and have a problem with my first layout design. I am trying to design layout, schematic and symbol, and then using symbol or schematic to test my design.

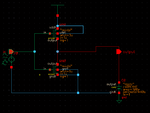

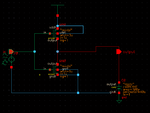

Here is the schematic:

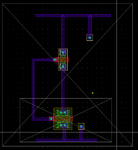

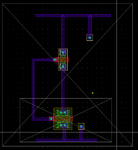

And here is the layout I designed:

When I run DRC, I get the following warnings:

Why does it still say that I have "not stamped connections"?

I just registered for the forum and have a problem with my first layout design. I am trying to design layout, schematic and symbol, and then using symbol or schematic to test my design.

Here is the schematic:

And here is the layout I designed:

When I run DRC, I get the following warnings:

Why does it still say that I have "not stamped connections"?

Attachments

Last edited: