hardyboy_86

Junior Member level 2

Hi,

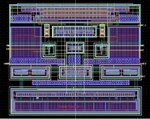

I have Layout the design of Gain Boosting Op_Amp but i am experiencing a major issue in post layout that its Unity Gain frequency is going below half of the total,

My gain boosting op_amp is designed for 1.3 GHZ with 77 Degree phase, but in post layout after every effort i managed to get it to 904 MHZ with 65 Degree of phase,,

Plz Let me know what steps should i take to resolve this issue.

Thanks Alot!!

I have Layout the design of Gain Boosting Op_Amp but i am experiencing a major issue in post layout that its Unity Gain frequency is going below half of the total,

My gain boosting op_amp is designed for 1.3 GHZ with 77 Degree phase, but in post layout after every effort i managed to get it to 904 MHZ with 65 Degree of phase,,

Plz Let me know what steps should i take to resolve this issue.

Thanks Alot!!