nanostallmann

Newbie level 5

Hi all,

I have a question about a phase accumulator that I'm doing for implement a DDS in an ATLYS board (SPARTAN6).

The phase accumulator that I wrote works with a input 18bit phase_word_width and outputs a 10bit address to a RAM block.

When I set a phase word that set integer or fractional part (ie: 000000001000000000 or 000100000000000000 or 000000000010000000)

the accumulator outputs the values with constant increment (ie: 2 each clock period, 64 each clock period or 1 every two clock period for the ie above).

When I set a phase word that set either integer and fractional part ( ie: 000000000110000000) the accumulator outputs the sequence with variable increment (ie: one time with 1 increment and 1 time with 2 increment).

Mathematically I think is ok! but the question is:

When I change the phase with variable increment the wave will not distorted by spurs generated by this behavior???

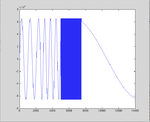

For clarity there are some simulation screen-shoots (the example above don't respect the simulation values):

I think that one solution could be interpolate the output values... what your opinion about this ??

Thank you

I have a question about a phase accumulator that I'm doing for implement a DDS in an ATLYS board (SPARTAN6).

The phase accumulator that I wrote works with a input 18bit phase_word_width and outputs a 10bit address to a RAM block.

When I set a phase word that set integer or fractional part (ie: 000000001000000000 or 000100000000000000 or 000000000010000000)

the accumulator outputs the values with constant increment (ie: 2 each clock period, 64 each clock period or 1 every two clock period for the ie above).

When I set a phase word that set either integer and fractional part ( ie: 000000000110000000) the accumulator outputs the sequence with variable increment (ie: one time with 1 increment and 1 time with 2 increment).

Mathematically I think is ok! but the question is:

When I change the phase with variable increment the wave will not distorted by spurs generated by this behavior???

For clarity there are some simulation screen-shoots (the example above don't respect the simulation values):

I think that one solution could be interpolate the output values... what your opinion about this ??

Thank you

Last edited: