KillaKem

Junior Member level 2

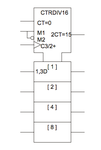

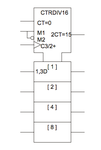

I want to design a synchronous counter with 12 states and synchronous reset by connecting the overflow signal ( CT =15 ) directly to load input ( /M2M1 ) so that I can start the counter at a custom state, what I'm thinking of doing right now is just put flip-flops pre-loaded with my predefined start state at the input of the counter so that the state is loaded when ever the load signal goes high, but I don't know if this is the easiest route to take, does someone know how I can do this in the easiest way possible? How would I implement this in verilog / system verilog?