wdssll

Newbie level 6

Hi all,

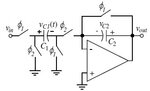

during the simulation of the sample and hold circuit, i have encountered one problem. the circuit is a simple sample and hold circuit consisting of a switch and a capacitor. the input is vsin with pac mag set to 1. after simulation, when the sampled voltage at the capacitor becomes 0.5 instead of 1.

when i ran trans simulation, the sampled voltage matches with the input sine wave.

anyone has any idea why the sample voltage becomes half during the pac simulation?

thanks very much for your help

during the simulation of the sample and hold circuit, i have encountered one problem. the circuit is a simple sample and hold circuit consisting of a switch and a capacitor. the input is vsin with pac mag set to 1. after simulation, when the sampled voltage at the capacitor becomes 0.5 instead of 1.

when i ran trans simulation, the sampled voltage matches with the input sine wave.

anyone has any idea why the sample voltage becomes half during the pac simulation?

thanks very much for your help