richipedia

Newbie level 4

- Joined

- Oct 24, 2012

- Messages

- 5

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Location

- NRW, Germany

- Activity points

- 1,326

Hello everybody,

I am working on an application in which I need to employ a discrete MOSFET as a switch to block voltages of both polarities. I have already learned that because of the body diode, two MOSFETs connected in an anti serial manner must be used.

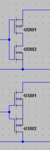

Now there are two possibilities: (see the picture below)

1. Connect both gates and both sources to form the switch. This is known as "source mating". (bottom of the picture)

2. Connect both gates and both drains to form the switch. This is known as "drain mating". (top of the picture)

Which option should be preferred, and why?

I am working on an application in which I need to employ a discrete MOSFET as a switch to block voltages of both polarities. I have already learned that because of the body diode, two MOSFETs connected in an anti serial manner must be used.

Now there are two possibilities: (see the picture below)

1. Connect both gates and both sources to form the switch. This is known as "source mating". (bottom of the picture)

2. Connect both gates and both drains to form the switch. This is known as "drain mating". (top of the picture)

Which option should be preferred, and why?