Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

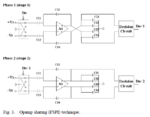

in Razavi's CMOS book Chapter 12, see figure below

View attachment 82262

how to bias the opamp properly since the opamp is configured with capacitive feedback (C2) at both phases?

thanks!

Normally, such a circuit (classical S/C integrator topology) is used not as a stand-alone circuit but it is a part of an overall negative feedback loop (filter circuit).

In these cases, no special bias considerations are required. This is the same situation as for continuous time integrators, which also cannot be operated without an overall negative feedback loop.

It is a switched-capacitor circuit. The switched capacitors, which are switched at a much higher speed than the signal frequency, simulate resistors, i.e. the charge carried through the switched capacitor is proportional to the voltage across the switched-capacitor circuit. The equivalent resistance of the switched capacitor circuit is inversely proportional to the switching speed times the capacitor size. Thus, the integrator is biased the same as if the switched-capacitor input was actually a resistor.

Switched capacitors are used in ICs because it's easier and takes less space to build precision capacitors then it is precision resistors in the standard IC process.

Hi crustchow, thanks for your reply. yes, it's SC circuit, i know its application and its block diagram function. just one doubt about how to DC bias the opamp with feedback, or just as LvM said there is no need to use feedback to bias the opamp here in this case,....

Just in order to avoid a misunderstanding: There is no need for separate bias considerations if the S/C integrator is used as one element in a closed negative feedback loop which contains also other stages (like in active S/C filters).

here i am trying to do opamp sharing in a pipeline ADC, it is cascade stages, but there is no feedback like the case i said before.

i have to think more, since the opamp is working(at amplification mode for stage one and stage two) at both phases, there is no time for another SC as a resistor, i think....In this case, I think, you should follow the same guidelines as in the analog domain: Use a damped (lossy) integrator (Resistor Rp in parallel to the feedback C) which resembles a 1st order low pass filter.

In the sampled-data domain (S/C technique) the resistor Rp is, of course, realized as another switched capacitor.

Could this cure your problem?

What is the purpose of the integrator in the pipeline ADC? Don't you just need the op amp as an amplifier?..............................

here i am trying to do opamp sharing in a pipeline ADC, it is cascade stages, but there is no feedback like the case i said before.

it's not used as the purpose of integrator but it will have the same configuration like the integrator figure (there is a cap at both phases there ) mentioned above during both phases for stage 1 and stage 2 in the pipeline if the opamp is shared.What is the purpose of the integrator in the pipeline ADC? Don't you just need the op amp as an amplifier?

it's not used as the purpose of integrator but it will have the same configuration like the integrator figure

I think, when a circuit has the configuration of an integrator (with or without intention) it will work as an integrator, will it not?

Looking at the schematic, it seems obvious that it's simplifying things a bit. No MOSFET or BJT amplifier can work without a switched or continuous input bias path. I don't think that it makes sense to discuss circuit details at this level of superficial knowledge.