kothandapani

Junior Member level 3

Hi,

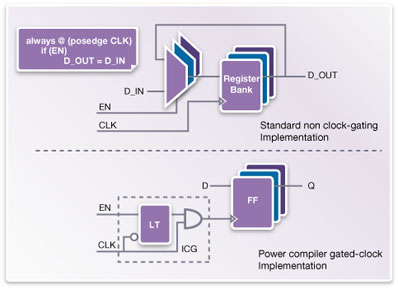

Why the Clock gating cells are added in a Design ?

As per I know the clock gating cells are added during 1. RTL stage of design and 2. During the Synthesis stage of design

1. How it will be desided to add clock gating cells durin RTl stage and where exactly it will be added in a design?

2. Who will be desided to add the clock gating cells during Synthesis and what basis it will be added during synthesis?

3. In the core netlist (before scan inserted netlist) all the clock gating cells are added and then how these are handeled during scan stiching?

Why the Clock gating cells are added in a Design ?

As per I know the clock gating cells are added during 1. RTL stage of design and 2. During the Synthesis stage of design

1. How it will be desided to add clock gating cells durin RTl stage and where exactly it will be added in a design?

2. Who will be desided to add the clock gating cells during Synthesis and what basis it will be added during synthesis?

3. In the core netlist (before scan inserted netlist) all the clock gating cells are added and then how these are handeled during scan stiching?