pmtwiss

Junior Member level 2

- Joined

- May 28, 2008

- Messages

- 21

- Helped

- 2

- Reputation

- 4

- Reaction score

- 2

- Trophy points

- 1,283

- Location

- Pasadena, CA

- Activity points

- 1,502

Hello,

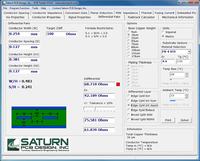

I am interested in how to find a good way to route differential pairs in the internal layers. This normally is a good idea except the fact now you have 2 reference planes, in which most tools can not calculate this b/c they are not set up to. Example is using the Saturn PCB toolkit to calculate differential pair calculations. It only give you a single reference plane. It would be nice ot be able to prdict what would happen to some accuracy when routing in internal layers as you can get good shielding this way.

Can someone add some experience or some advice or method for accurately calculating impedance on internal layers? Last time I used hyperlynx SI it couldn't do it =/

Thanx,

-Peter

I am interested in how to find a good way to route differential pairs in the internal layers. This normally is a good idea except the fact now you have 2 reference planes, in which most tools can not calculate this b/c they are not set up to. Example is using the Saturn PCB toolkit to calculate differential pair calculations. It only give you a single reference plane. It would be nice ot be able to prdict what would happen to some accuracy when routing in internal layers as you can get good shielding this way.

Can someone add some experience or some advice or method for accurately calculating impedance on internal layers? Last time I used hyperlynx SI it couldn't do it =/

Thanx,

-Peter