samiran_dam

Full Member level 2

Hi all,

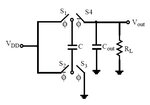

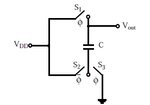

It would be very helpful if somebody review my explanation about the operation of this ideal voltage doubler based on charge pump shown in the following figure:

In Phase-1 (when Φ=1): S1 and S3 are closed and S1 is open - the capacitor is connected between the VDD and the ground.

The capacitor charges up to voltage VDD and the output (floating) is VDD

In Phase-1 (when Φ=0): S1 and S3 are open and S1 is closed - the capacitor's bottom plate is connected to VDD and top plate to the floating output node.

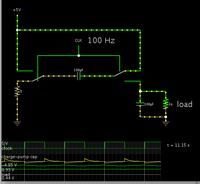

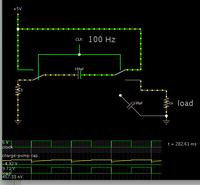

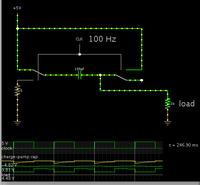

Initially output voltage is 2VDD as the voltage across the capacitor is VDD. But the capacitor will start charging up in the opposite direction so steady state value at output is 0. But it will be not observable in time-domain plot because there is no resistive path so the capacitor charges up to the opposite polarity instantaneously. If I connect a resistance (R) at the output node then it can be seen that the the output discharges from 2VDD to 0 with RC time-constant.

Am I correct? If not please explain.

Sam.

It would be very helpful if somebody review my explanation about the operation of this ideal voltage doubler based on charge pump shown in the following figure:

In Phase-1 (when Φ=1): S1 and S3 are closed and S1 is open - the capacitor is connected between the VDD and the ground.

The capacitor charges up to voltage VDD and the output (floating) is VDD

In Phase-1 (when Φ=0): S1 and S3 are open and S1 is closed - the capacitor's bottom plate is connected to VDD and top plate to the floating output node.

Initially output voltage is 2VDD as the voltage across the capacitor is VDD. But the capacitor will start charging up in the opposite direction so steady state value at output is 0. But it will be not observable in time-domain plot because there is no resistive path so the capacitor charges up to the opposite polarity instantaneously. If I connect a resistance (R) at the output node then it can be seen that the the output discharges from 2VDD to 0 with RC time-constant.

Am I correct? If not please explain.

Sam.

Last edited: