frankqt

Member level 4

Improving SNR using DSP

I am building an optical OOK (On off Key Ring) system without a carrier frequency. [However I have a guard time in between symbols, so a consecutive "1" messages will result in a pulse train as opposed to DC]. Essentially, the presence of signal indicates one and lack of it indicates zero. I have a precise clock that is synced with transmitter. The system operates with a low SNR and I like to improve SNR using DSP techniques.

I have a few questions:

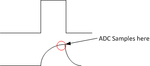

I do selective sampling in my hardware, in other words, I do not continuously sample the channel but only sample when the probability of seeing the signal is maximum (i.e. this is a light pulse, I time the ADC such that ADC samples at the end of the pulse where I know the whole analog chain is stabilized). See image.

Naturally, this drawing doesn't show the noise but it is there. The noise is mostly shot noise, johnson noise, opamp noise etc. I now use a simple threshold comparison in software to determine if the data is one or zero. Is there a better way? I have thought of some options but I like to hear from the experts.

So far I have considered the following options:

I am building an optical OOK (On off Key Ring) system without a carrier frequency. [However I have a guard time in between symbols, so a consecutive "1" messages will result in a pulse train as opposed to DC]. Essentially, the presence of signal indicates one and lack of it indicates zero. I have a precise clock that is synced with transmitter. The system operates with a low SNR and I like to improve SNR using DSP techniques.

I have a few questions:

I do selective sampling in my hardware, in other words, I do not continuously sample the channel but only sample when the probability of seeing the signal is maximum (i.e. this is a light pulse, I time the ADC such that ADC samples at the end of the pulse where I know the whole analog chain is stabilized). See image.

Naturally, this drawing doesn't show the noise but it is there. The noise is mostly shot noise, johnson noise, opamp noise etc. I now use a simple threshold comparison in software to determine if the data is one or zero. Is there a better way? I have thought of some options but I like to hear from the experts.

So far I have considered the following options:

- Do continuous ADC and try to integrate during rise time:Not entirely sure on the benefit (There may be other benefits, I don't know)

- Matched filter in software: Don't really understand the math but based on what I read, a possibility

- Sample during the guard time and subtract this from the signal ADC value (This may provide some further details but also not so sure, guard time would be the noise measurement)

- Change hardware to a synchronous decoder, costly, time consuming and may not work well since my data rate is fast and getting a synchronous demodulator would mean expensive board since I have to built a multi-MHz carrier frequency system.

Attachments

Last edited: