owen_li

Full Member level 3

Hi all.

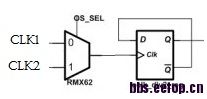

I have a below schematic:

there are two clocks named clk1 and clk2. Then they are selected by a mux, then the output clock is divided by a two divided register.

Then the output of the register is used as the main clock for the following logic.

Also, there are some logic feeded by clk1 and clk2.

So could you tell me how to code the sdc for this scenario ?

Thanks all!

I have a below schematic:

there are two clocks named clk1 and clk2. Then they are selected by a mux, then the output clock is divided by a two divided register.

Then the output of the register is used as the main clock for the following logic.

Also, there are some logic feeded by clk1 and clk2.

So could you tell me how to code the sdc for this scenario ?

Thanks all!