wuxy

Junior Member level 1

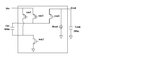

In the design the voltage doubler is used to power internal circuits.Two CAP are external.

simulation show big spikes on Vout when wire induction is took in account, especially at the transition from transfer phase to charge phase, a big minus spike occur.

Do the switching sequence or the rising speed of the switch driving signal have effect?

Could anybody give me some help ?