Ayyanar M

Junior Member level 1

PLL---> Problem on locking @ 500MHz

Hi,

See the attachment and give me a solution.

Issue related to each one)

related to each one)

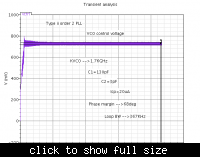

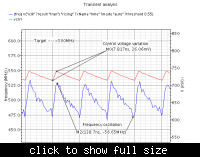

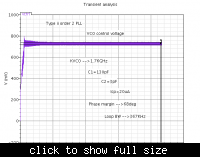

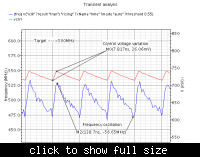

1) There is no variation in the VCO control voltage after the settling time reached(Equal charging and discharging occurs)

2) Up error only maintaining after the settling time(There is no down error)

3) Frequency is oscillating @ 470MHz<500MHz<530MHz(see the attachment)

problem is more but solution is only one(I think so)

Hi,

See the attachment and give me a solution.

Issue

1) There is no variation in the VCO control voltage after the settling time reached(Equal charging and discharging occurs)

2) Up error only maintaining after the settling time(There is no down error)

3) Frequency is oscillating @ 470MHz<500MHz<530MHz(see the attachment)

problem is more but solution is only one(I think so)

Last edited: